# **PICMG 1.3**

The PICMG 1.3 allows users to protect their investment in PCI technology while taking advantage of the speed and increased bandwidth of PCI Express

## What is PICMG 1.3?

• Bringing PCI Express to your SBC with increased speed and bandwidth

PICMG 1.3 is designed to interface with PCI Express peripherals on a backplane. The PCI Express interconnects with the backplane and can operate at x1, x4, x8, x16, and more, depending on the capabilities of both the SHB and the backplane.

Support PCI on board with flexibility

The optional PCI portion of the SHB interconnected with the backplane allows for 32-bit operation. The clock rate can be 33 MHz, 66 MHz, 100 MHz, and 133 MHz, depending on how the backplane and SHB are designed.

Miscellaneous IO

SATA, USB, IPMB, SMBus, Geographic Addressing, and PCI Wake Up to the backplane are specified, simplifying the cabling on SHB for the system.

# PICMG 1.3 Key Features

PCI Express

20 PCI Express lanes are supported, including PCI Express x16, x4 and x1 configurations

• ATX power signals are supported

Provides AUX voltages for standby power and sleep states (soft starts, wake on LAN), supports PSON#, PWRGD, PWRRBT# and ACPI states

# Why PICMG 1.3?

- This new technology is expected to allow PCIe transmission rates to keep pace with processor and I/O advances for the next 10 years or more.

- Same basic mechanical dimensions are maintained to minimize chassis redesign expense

- Better host board power management and simplified I/O cabling

- Supports PCI Express and PCI option cards without driver changing

# The future will be.... Faster CPU Faster chipsets & system busses Chipsets are migrating toward PCI Express

# **Graphic & Server Grade PICMG 1.3 Solutions**

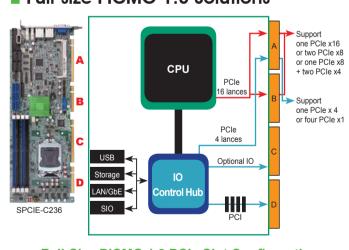

# Full-size PICMG 1.3 Solutions

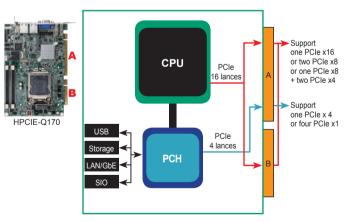

# ■ Half-size PICMG 1.3 Solutions

# **Full-Size PICMG 1.3 PCle Slot Configuration**

| Full-size SBC Type                   |              |     | Server &<br>Graphic Grade |   | Server Grade        |   |   |   |

|--------------------------------------|--------------|-----|---------------------------|---|---------------------|---|---|---|

| Combination                          |              |     | Α                         | В | С                   | D | E | F |

| PCIe Slots Available<br>(Non-switch) | CPU<br>or NB | x16 | 1                         | 1 | -                   | - | - | - |

|                                      |              | x8  | -                         | - | 2                   | 2 | 1 | 1 |

|                                      |              | х4  | -                         | - | -                   |   | 2 | 2 |

|                                      | PCH<br>or SB | х4  | -                         | 1 | -                   | 1 | - | 1 |

|                                      |              | x1  | 4                         | - | 4                   | - | 4 | - |

| Backplane Solution                   |              |     | IEI PE/PXE series         |   | IEI SPE/SPXE series |   |   |   |

### Half-Size PICMG 1.3 PCIe Slot Configuration

| Half-size SBC Type                   |     |     | Any Type |   | High Performance |   |   |   |

|--------------------------------------|-----|-----|----------|---|------------------|---|---|---|

| Combination                          |     |     | Α        | В | С                | D | E | F |

| PCIe Slots Available<br>(Non-switch) | СРИ | x16 | 1        | 1 | -                | - | - | - |

|                                      |     | x8  | -        | - | 2                | 2 | 1 | 1 |

|                                      |     | x4  | -        | - | -                |   | 2 | 2 |

|                                      | PCH | x4  | -        | 1 | -                | 1 | - | 1 |

|                                      |     | x1  | 4        | - | 4                | - | 4 | - |